# Dynamically Reconfigurable RISC Microprocessor design using MIPS Instruction Set

Neethu K Krishnan<sup>#1</sup>, Bhavya Das D<sup>\*2</sup>

<sup>#1</sup>M tech Student ,Nehru College of Engineering and Research Center ,Pampdy,Thrissur,Kerala,India <sup>#2</sup>Assistant Professor,Nehru College of Engineering and Research Center ,Pampdy,Thrissur,Kerala,India

Abstract: Today's world suggests multifunction in each products. This paper design a RISC processor using MIPS instruction set architecture which supports multifunctioning. Dynamic Reconfiguration refers to the ability of the Processor to update its internal Instruction Decode and Execute stage in order to support new functions, while the system is running. This project presents a principle on how performance can be improved in the context of microprocessor Units applications, using the MIPS instruction set.

**Keywords** - *RISC*, *MIPS*, *dynamically reconfigurable*.

## I. INTRODUCTION

MIPS can be abbreviated as Microprocessor without Interlocked Pipelining Stages. It was first developed by Sony, Nintendo and NEC. It was developed to overcome the problems of the conventional design i.e. using same instruction set for all the applications makes instruction set busy and system a delaying system. MIPS processor core assigned different formats for certain instructions for their easy implementation.

RISC CPU have more advantages, such as reduced number of instructions, faster speed, and simplified structure easier implementation. RISC CPU is extensive use in embedded system. RISC processor has a load store load instruction.

This paper is a zoom in on how the MIPS instruction Set is embedded in an RISC Processor by increasing the performance.

# **II.** LITERATURE SURVEY

In this section we briefly review some of the works of designing RISC static processors.

In the scheme presented in [1] ensure the power reduction of a RISC processor .Here they created a RISC processor using MIPS architecture .They included clock gating and multi Vt technique to reduce the power. They have also incorporated hazard detection unit to remove the hazards if any. In the paper [2] a RISC processor has been designed in FPGA. They adopted top-down design method and use VHDL to describe system. They analyzed MIPS instruction format, instruction data path, decoder module function and design theory based on RISC CPU instruction set.

In the section [3] Stall in MIPS architecture has been reduced to maximum. Stall frequently happens in pipeline architecture which results in larger clock cycles. Here they reduced stall by introducing pre-fetching unit.

Another work [6] propose a 16-bit non-pipelined RISC processor, which is used for signal processing applications with 24 instruction set.

## III.PROPOSED WORK

## A. MIPS PROCESSOR ARCHITECTURE

Architecture of MIPS RISC microprocessor includes, fix-length straight forward decoded instruction, memory access is limited to load and store instruction format, a large general purpose register file.

The 32 bit RISC MIPS processor has 5 stages.

- 1. Instruction fetch (IF)

- 2. Instruction Decode (ID)

- 3. Execution (EXE)

- 4. Data memory (MEM)

- 5. Write back (WB)

The MIPS single cycle processor performs the tasks of instruction fetch, instruction decode, execute and memory access and write back all in one clock cycle.

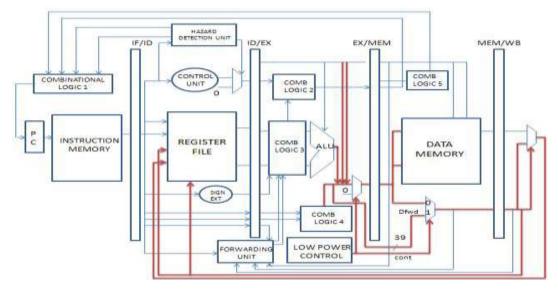

The architecture of RISC processor is shown in fig 1 with all the 5 Stages. Pipeling improves the performance of the processor

Fig 1: Block Diagram of RISC processor

# **B. DYNAMIC PROCESSOR**

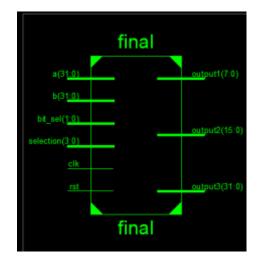

Processor that can automatically configure is called dynamic processor. Here the processor has been designed as 8 bit processor, 16 bit processor and 32 bit processor. According to our need we can reconfigure our processor.

By providing selection lines we can select the corresponding processor. We have provided 2 bit selection line.

- 01--8 bit processor

- 10--16 bit processor

- 11—32bit processor

In real time projects it provides the flexibility to switch between the processors.

Fig 2: Schematic view of dynamic processor

Algorithm:

- 1. Accept the inputs as 32 bit

- 2. Select the processor.

- 3. If the processor is 8 bit, Load 8 bit LSB of inputs.

- 4. If the processor is 16 bit, Load 16 bit LSB of inputs.

- 5. If the processor is 32 bit, load the complete value.

- 6. Select the instruction.

- 7. All the values are fetched, decoded and executed.

- 8. The result will be stored in the output register

- 9. According to the processor selection only the corresponding set of registers will be active.

10. The output will be displayed in corresponding 8 bit,16 bit,32 bit output lines.

# C. FPGA IMPLEMENTATION

The processor is synthesized in Xilinx FPGA. Field programmable gate array.

# **IV.RESULTS**

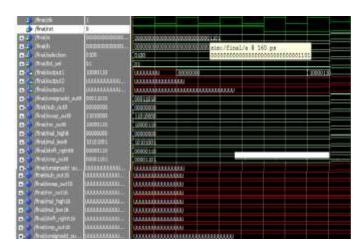

The Processor is designed in VHDL ,simulated with ModelSim. The synthesis tool Xilinx Spartan - 3E was used to verify results and for implanting the work in FPGA.

| D-2 - monaictor       | 180120                                   | A1#                                     | يصدر كالت والمارك           |

|-----------------------|------------------------------------------|-----------------------------------------|-----------------------------|

| p4 matest             | <b>II</b>                                | 12                                      | يسير ومعارجها والمراج       |

| D C Postadart         | HE#39                                    | 0000000 0000000                         | ويعتر ويعتر ويعتد ويعتد     |

| B. Delinger?          | #1000000111E                             |                                         | 0000000000000110            |

| Dia Dessert.          | anna ann an a |                                         |                             |

| D Retrepeti MP        | anna -                                   | 000000                                  |                             |

| D mana mil            | uuuuz                                    | 0000000                                 |                             |

| D fraiber, soll :     | LEAAAEEE                                 | UXXXXQ)                                 |                             |

| Dis Anticati          |                                          | uuuuuu                                  |                             |

| D D manual hybrid     | 4000333                                  | www.                                    |                             |

| a 👌 insind just       | 10.0.0.0                                 | 142444440                               |                             |

| D-S Huben_rgetz       | TAXABABA C                               | 0000000                                 |                             |

| D- Theore and         | annan                                    | www.w                                   |                             |

| D. Pollenguit         | (*************************************   | 0808000998081333.8                      | المدار المحد المحد المحد ال |

| 🖬 🍮 ANNINA DATIK      | 000000000000000000                       | 00000000000000                          |                             |

| Gel finitives, et al. | 000012200000000                          | 1000011010000000                        |                             |

| B Prefer_m232         | 1 mm m concerce ou 10                    | 100000000000000000000000000000000000000 |                             |

| D. Fining httl        |                                          | , Secessadd (1997)                      |                             |

| B mental in 2         | 00000000000000000000000000000000000000   | 000000000000000000000000000000000000000 |                             |

| D . theight subtis    | ALC HOLD ADDRESS OF                      | 000000000000000000000000000000000000000 |                             |

| D helling_odds        | 000000000000000000000000000000000000000  | 000000000000000000000000000000000000000 |                             |

| E                     |                                          |                                         |                             |

| P Inclui was          | uuuuuuu.                                 |                                         |                             |

| D - March and a state |                                          |                                         |                             |

| D RHER ALL            |                                          |                                         |                             |

Fig 3: 8 bit RISC processor

Fig 5: 32 bit RISC processor

#### V. CONCLUSIONS

The proposed system is designed for better performance. The processor was successfully designed in Verilog HDL, simulated with ModelSim 10.4 and synthesized on to a Xilinx Spartan-3E for FPGA implementation. The system can be rec

configured itself while the processor is running Future work can be done by adding number of instructions .

#### ACKNOWLEDGMENT

I am thankful to my guide Mr. Ershad E.B, Assistant Professor in department of Electronics and communication Engineering, NCERC, Pampady, Kerala ,India for the successful completion of my project.

I thank all my friends and family members for their support and consideration for the completion of this work.

#### REFERENCES

- P.V.S.R.Bharadwaja, K. Ravi Teja, M.Naresh babu, K.Neelima (2015, May 20-21) Advanced Low Power RISC Processor Design using MIPS Instruction, *IEEE International Conference On Recent Trends In Electronics* and Communication systems.

- [2] Gautham P, Parthasarathy R, Karthi Balasubramanian (2014) Low-Power Pipelined MIPS Processor Design .

- [3] Mrs. Rupali S. Balpande. Mrs.Rashmi S. Keote. (2014,May) Design of FPGA based Instruction Fetch & Decode Module of 32-bit RISC (MIPS) Processor, 2011 International Conference on Communication Systems and Network Technologies

- [4] Panjali S Kalgoankar, Prof. Shilpa. Kodgire Design of 32 bit MIPS RISC Processor based on SoC, International journal of latest trends in Engineering and technology(IJLTET)

- [5] Zulkifli.M, Yudhanto, Y.P, Soetharyo NAdionoT Reduced Stall MIPS Architecture using Pre-Fetching Accelerator., 2009 International Conference on Electrical Engineering and Informatics5-7 August 2009, Selangor, Malaysia

- [6] R.Uma,"Design and Performance Analysis of 8-bit RISC Processor using Xilinx Tool"2012 International Journal of Engineering Research and Applications (IJERA)

- [7] Anand Nandakumar Shardul, "16-Bit RISC Processor Design for Convolution Application", -2013 International Journal of Advancements in Research & Technology.

- [8] Ciletti, Michael D. "Advanced Digital Design with the Verilog HDL."Upper Saddle River, NJ: Pearson Education Inc. 2003

- [9] Sagar Bhavsar, Akhil Rao, Abhishek Sen, Rohan Joshi," A 16-bit MIPS Based Instruction Set Architecture for RISC Processor" April 2013 International Journal of Scientific and Research Publications.

- [10] V. B. Saambhavi and V. S. Kanchana Bhaaskarana," 16-bit RISC microprocessor using dcpal circuits" International Journal of Advanced Engineering Technology

- [11] .Dalal, A.Ganesh, Aishwarya.D "An 8 bit Power-Efficient MIPS Processor " Advanced VLSI Design Sping 2014