# Efficient Pixel Architecture of CMOS Image Sensor using CMOS 180 nm technology

Dipti<sup>1</sup>, Rajesh Mehra<sup>2</sup>, Deep Sehgal<sup>3</sup>

<sup>1</sup>Student ME (Regular)-ECE Department, NITTTR, Chandigarh <sup>2</sup>Associate Professor of ECE Department, NITTTR, Chandigarh <sup>3</sup>Sci/Engr 'SE', SCL, Mohali

**Abstract-** This paper describes CMOS Active Pixel Sensor (APS) that has huge demand in imaging systems. The pixel architecture consists of number of NMOS transistors and reverse biased p-n junction diode act as photo sensing element designed in 0.18um CMOS technology. The  $(64^{H}X64^{V})$  pixel array have presented and described. The sensor design contains 5T pixel architecture to investigate the effects by measuring its parameters. The Image Sensor presented in this paper achieves better well capacity, voltage swing and conversion gain. The measured results of sensor have pixel bucket with capacity of (28089 e<sup>-</sup>), voltage swing of (1.2V) and conversion gain of (79.1uV/e<sup>-</sup>). By measuring these parameters, the presented pixel architecture can be optimized for several applications.

**Index terms-** *CMOS Image Sensor (CIS), Active Pixel Sensor (APS), Photodiode.*

## I. INTRODUCTION

In large scale system design, CMOS Image Sensor plays a significant role in imaging systems suitable for different purposes and it has greater demand in market of imaging system [1]. CMOS Image Sensor (CIS) have rapid developments than CCD due to its number of advantages. These are generally higher speed and have larger data throughput as compare to CCD technology, There are such applications of CMOS Image Sensor (CIS) i.e. fluorescence, spectroscopy, time-of-flight imaging, radiation therapy, proton radiography and blue free projectile tracking [2]. There have been several researches done to improve the parameters to produce the high performance Image Sensor. So many applications areas caused that CMOS technology breakthrough on two fronts in 2000: sensors for computers and cell phones on the low end, and ultra high speed, large format imaging on the high end. Moreover, new technologies and architectures appeared due to scale effects [3]. In the world of technology, the demand of CMOS devices rising day by day and their popularity depends on small area and long life time with optimized parameters. So, devices must be design to be used in application by consuming less power [4]-[6]. Technology scaling of CMOS design is one of the driver behind improvement in performance in the integrated circuits [7]-[8]. The CMOS Imager can be voltage mode and current mode. Current mode of CMOS Imager have disadvantage of

poor linearity and high fixed pattern noise as compare to the voltage mode CMOS Image Sensor [9]. The Image Sensor of high charge collection efficiency with better conversion gain is often required by scientific, commercial and consumer applications [10]. CMOS Active Pixel Sensor (APS) technology was originally considered as inferior, later improvements in such parameters of Image Sensor i.e. Cost, Power consumption, Dynamic Range, blooming effect, readout scheme, speed and smartness have occurred to achieve high performance equal to or better than CCD technology [11]. Novel technologies coming into focus to provide integration [12] of imaging and processing functions on a single chip, reducing cost and size of CMOS Image Sensor. The traditional imaging readout function enables quick processing of images [13]. In CMOS Active Pixel Sensor (APS), the major source of noise is the reset noise that is occurred when the sense node capacitance is reset [14]. CMOS APS (Active pixel sensor) is made to improve scalability to the large array formats and higher speed readout as compare to the Passive pixel sensors. In CMOS Active Pixel Sensor array, the pixel area is constructed of two functional parts. The first part consist of geometrical shape of sensing element: act as active area to absorb incident illumination energy and convert that energy into charge carriers in silicon substrate. The second part described by control circuitry designed used for readout operations using NMOS transistors because there is no requirement of n-well layer in NMOS transistors. Due to this feature, it consumes less area as compare to the PMOS transistors [15]. In this paper, the CMOS Active Pixel Sensor designed in 0.18um, 3.3V CMOS process consists of 64X64 pixel array with row decoder and column decoder. The array employs pixel level parameters have been measured and optimized. This paper also focuses on the reset noise. In equation form, the reset noise [in volts root mean square (rms) is  $\sigma_{\text{reset}}(V) = \sqrt{KT/C}$  or, in e units  $\sigma_{\text{reset}}(e) =$  $\sqrt{\mathit{KTC}}$  , where C is capacitance of sense node, T is

temperature and q is electron charge. The well capacity and conversion gain are of concern. In pixel structure, large well is required, so that blooming effect can reduced to prevent charge overflow from pixel bucket that starts to fill adjacent pixel.

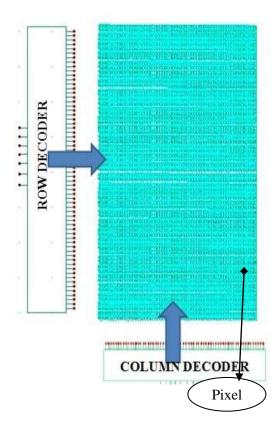

Fig.1 - Block of CMOS Image Sensor

The system architecture of CMOS Image Sensor is shown in fig.1. It consists of Pixel array with number of rows and columns. Row and column decoder implemented by decoder for scanning pixels in the array. Row decoder is Y-addressing line to select the particular row of the pixel array. Column decoder is X-addressing line to read out the column busses that connect the select row the pixel.

#### II. PIXEL DESCRIPTION AND OPERATION

The pixel act as picture element forms basic unit of image sensor consist of detector and readout circuit to make complete transfer of charge to the external terminal for data acquisition [16].

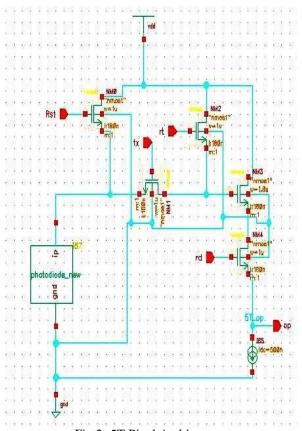

### A. The 5T Pixel Architecture

5T pixel is a variation of 4T pixel that is solving several issues related to imager with four transistors. The main drawback of 4T transistor is due to slightly shifting of start and stop duration of exposure which results to image deformation for fast moving objects. The design of 5T is quite similar to the 4T architecture, except for extra reset transistor to reset all rows simultaneously and for exposure control. The pixel circuitry shown in fig. with single reverse-biased p-n-junction diode (PD) for incident photon conversion to charge, and five transistors i.e. the photodiode reset transistor (M1), transfer gate (M2) to make complete transfer of charge generated by the incident photon during integration period, Floating diffusion reset transistor (M3) to reset floating

diffusion node for the next period of integration, Source follower transistor (M4), Row select transistor (M5). There are two major components of junction capacitance of the photodiode: bottom plate and side wall. Both of these components play an important role in the performance of the Active pixel sensor.

Fig.2- 5T Pixel Architecture

# B. Operating modes of APS

There are three operating modes for Active Pixel Sensor: Reset mode, Integration mode, Readout mode. These modes of operation works sequentially for every cycle until the entire rows of array are read out at the column line.

- 1) Reset mode: Initially, the reset transistor M1 and M3 reset the photodiode and floating diffusion node simultaneously and reset values are readout at the column line.

- 2) Integration mode: The integration of incident photons starts after reset mode of operation. In this mode, photons are sense by photo sensing element. During this process, the transistor M2 (transfer gate) is on to transfer the photo charge from photodiode node to floating diffusion (FD) node, where FD node act as conversion and memory node because it convert charge to voltage and store charge transferred from FD node until, the RS (Row select) transistor is on.

3) **Read out mode:** In this mode, row select transistor is responsible for read out the signal through column line by scanning each row of the pixel array.

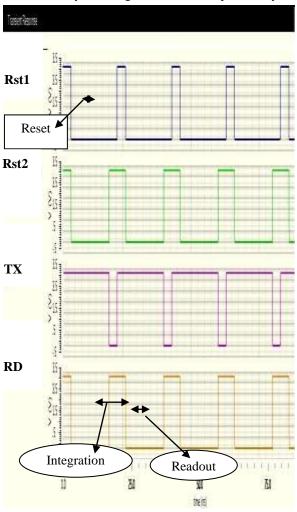

Fig.3- Control Signals for Pixel circuit

Fig.3 shows the waveform of control signals (Rst1, Rst2, TX, and RD) for pixel architecture, where Rst1 is photodiode reset signal, Rst2 is Floating diffusion reset signal, TX is signal for transfer gate and RD is control signal for row select signal. Initially, reset phase takes place. In this phase, Reset transistors (Rst1 and Rst2) are 'on' to reset the charge on photodiode and FD node and reset value is obtained by turning on the Row select transistor (RS). The calculated noise occurred due to reset transistor called Reset noise is 89e (in terms of e) and 0.28mV<sub>rms</sub> (in terms of voltage). In next phase, integration of incident illumination takes place. In this phase, the TX transistor is 'on' to transfer charge from PD to FD node. During this integration period, the row select transistor switch to off state. Charge is stored in the floating diffusion node and the accumulated charge convert into voltage in this node. After integration, this voltage is readout by turning on the RD transistor. During this phase, the Rst2 transistor again turns on to make double sampling at the output terminal. After

completion of one cycle, these three modes of operation again repeat for the next cycle of operation.

Fig.4- Output waveform for Pixel

The waveform in fig.4 shows the signal obtained on the output of Pixel. At the end of each cycle of pixel operation, two values are obtained i.e. reset value and signal value. Throughout the array, these two values are obtained on output with the column line by turning on their respective row select transistor.

## III. SIMULATION RESULTS

In this Paper, Spectre simulation is performed using Cadence virtuoso. This design is based on 0.18um CMOS technology.

**TABLE I**Measured performance of Pixel

| Parameter       | Paper [10] | This work |

|-----------------|------------|-----------|

| Technology (um) | 0.18       | 0.18      |

| Pixel Array     | 64X64      | 64X64     |

| Number of<br>transistors per<br>pixel            | 4     | 5     |

|--------------------------------------------------|-------|-------|

| Full well capacity (e <sup>-</sup> )             | 19200 | 28089 |

| Conversion<br>Gain at FD<br>(uV/e <sup>-</sup> ) | 69.3  | 79.1  |

| Signal swing (V)                                 | 1.067 | 1.2   |

#### IV. CONCLUSION

CMOS Image Sensor technology has excellent performance for the new generation of sensors. In this paper, CMOS Image Sensor (64<sup>H</sup>X64<sup>V</sup>) pixel array has been designed in 0.18um technology and simulated pixel architecture. The Pixel architecture of CMOS Image Sensor presented in this paper improves well capacity by (46.2%), voltage swing by (14.1%) and conversion gain by (12.4%). Future works in CMOS Image Sensor includes the optimization of Column level circuit of the pixel array.

#### REFERENCES

- [1] Zhiyuan Gao, Jiangtao Xu, Yiming Zhou and Kaiming Nie, "Analysis and Modeling of the Light-Dependent Full Well Capacity of the 4-T Pixel in CMOS Image Sensors", *IEEE Sensors Journal*, Vol. 16, No. 8, pp.2367-2373, April 2016.

- [2] Swetha S. George, Mark F. Bocko and Zeljko Ignjatovic, "Current Sensing-Assisted Active Pixel Sensor for High-Speed CMOS Image Sensors", *IEEE Sensors Journal* Vol. 15, No. 8, pp.4365-4372, August 2015.

- [3] Eric R. Fossum, and Donald B. Hondongwa, "A Review of the Pinned Photodiode for CCD and CMOS Image Sensors", *IEEE Journal of the Electron Devices Society*, Vol. 2, No. 3, pp.33-43, May 2014.

- [4] Anjali Sharma and Rajesh Mehra, "Area and Power Efficient CMOS Adder Design by Hybridizing PTL and GDI Technique", *International Journal of Computer Applications*, Vol. 66, No.4, March 2013.

- [5] Tanvi Sood and Rajesh Mehra, "Design a Low Power Half-Subtractor using .90μm CMOS Technology", IOSR Journal of VLSI and Signal Processing (IOSR-JVSP), Vol. 2, pp.51-56, May-June 2013.

- [6] Richa Singh and Rajesh Mehra, "Power Efficient Design of Multiplexer using Adiabatic Logic", *International Journal of Advances in Engineering & Technology*, Vol. 6, pp.246-254, March 2013.

- [7] M.Geetha Priya, K.Baskaran. "Low Power Full Adder With Reduced Transistor Count". *International Journal of Engineering Trends and Technology*, Vol. 4, pp.1755-1759 May 2013.

- [8] Pushpa Saini and Rajesh Mehra, "Leakage Power Reduction in CMOS VLSI Circuits", *International Journal of Computer Applications*, Vol. 55, No.8, pp.0975-8887, October 2012.

- [9] Fang Tang and Amine Bermak, "A 4T Low-Power Linear-Output Current-Mediated CMOS Image Sensor", IEEE Transactions On Very Large Scale Integration (VLSI) Systems, Vol. 19, No.9, pp.1559-1568, September 2011.

- [10] Rebecca E. Coath, Jamie P. Crooks, Adam Godbeer, Matthew D. Wilson, Zhige Zhang, Marcel Stanitzki, Mike Tyndel, and Renato A. D. Turchetta, "A Low Noise Pixel Architecture for Scientific CMOS Monolithic Active Pixel Sensors", *IEEE*

- Transactions on Nuclear Science, Vol. 57, No.5, pp.2490-2496, October 2010.

- [11] Thalis Anaxagoras, Paul Kent, Nigel Allinson, Renato Turchetta, Tim Pickering, Dzmitry Maneuski, Andrew Blue, and Val O'Shea, "eLeNA: A Parametric CMOS Active-Pixel Sensor for the Evaluation of Reset Noise Reduction Architectures", *IEEE Transactions on Electron Devices*, Vol. 57, No. 9, pp.2163-2175, September 2010.

- [12] Rajesh Mehra and Swapna Devi, "Area Efficient & Cost Effective Pulse Shaping Filter for Software Radios", International Journal of Ad hoc, Sensor & Ubiquitous Computing, Vol. 1, No.3, pp.85-91, September 2010.

- [13] Orly Yadid-Pecht, "CMOS Imager (From phototransconduction to Image Processing)", Kluwer Academic Publishers, 2004.

- [14] Suat Utku, "Photodiode Peripheral Utilization Effect on CMOS APS Pixel Performance", *IEEE Transactions on Circuits and Systems-I: Regular Papers*, Vol. 55, No.6, pp.1405-1411, July 2008.

- [15] Igor Shcherback and Orly Yadid-Pecht, "Photoresponse Analysis and Pixel Shape Optimization for CMOS Active Pixel Sensors", *IEEE Transactions on Electron Devices*, Vol. 50, No.1, pp.12-18, January 2003.

- [16] Karim S. Karim, Arokia Nathan and John Alan Rowlands, "Amorphous Silicon Active Pixel Sensor Readout Circuit for Digital Imaging", *IEEE Transactions On Electron Devices*, Vol. 50, No.1, pp.200-208, January 2003.